## ENGINEERING DESIGN FOR ELECTRICAL ENGINEERS

## Alan D. Wilcox

Micro Resources Company, Lewisburg, PA

## with

Lawrence P. Huelsman, University of Arizona

Stanley V. Marshall, University of Missouri, Rolla

Charles L. Phillips, Auburn University

Muhammad H. Rashid, Purdue University, Calumet

Martin S. Roden, California State University, Los Angeles

References

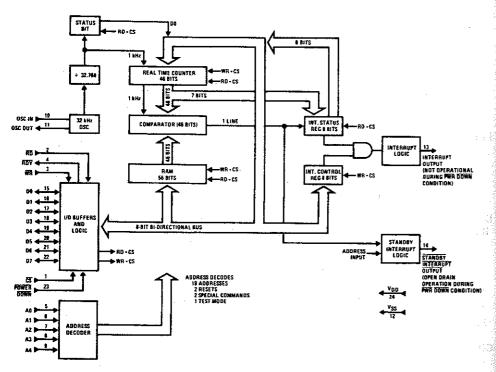

Figure 5.6 Block diagram of the MM58167A real-time clock. (Courtesy National Semiconductor Corp.)

normally completes within 500 ns. However, for I/O devices that require substantial access times; the bus cycle can be extended by adding a number of wait states, as in Figure 5.8. To find out if wait states are required during any read or write bus cycle, the bus master (the CPU) samples the RDY line at the rising edge of the system clock in Bus State 2 (BS2). If the RDY line is found low, then a wait state (BSw) is inserted immediately after BS2; if the RDY is still low a bus state later, then yet another wait state is inserted. Wait states continue to be added until RDY finally goes high; at that point, the bus cycle concludes with BS3.

The MM58167A clock requires wait states in the bus cycle because of its slow access time. For a clock-read operation, the time required from a valid address until the output data is valid might range from 500 ns to the specified maximum of 1050 ns, far longer than the time required for a normal bus cycle (i.e.,  $167 \text{ ns} \times 3 = 500 \text{ ns}$ ). The read cycle of a typical 6-MHz IEEE-696 system is shown in Figure 5.8, with approximate times to scale. Notice that the example timing diagram includes a total of three wait states to make up for the slow access time.

The normal S-100 requirement is that the RDY line be low at the end of BS1 if waits are required in a bus cycle. In the clock case, however, this is impossible: the clock

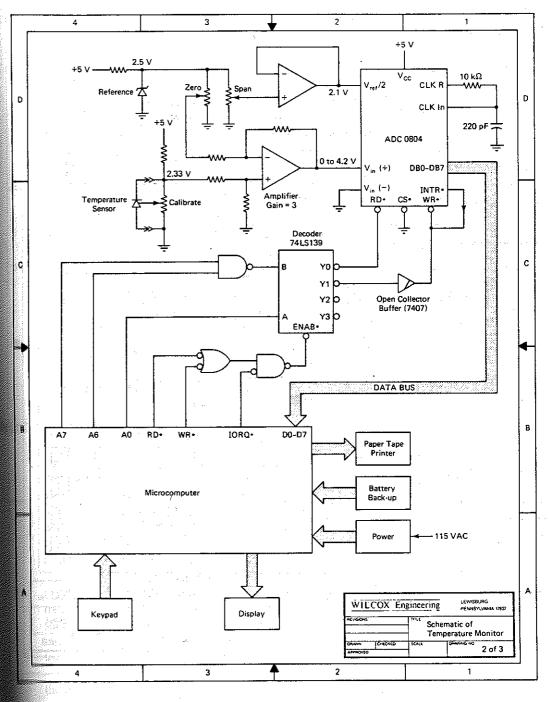

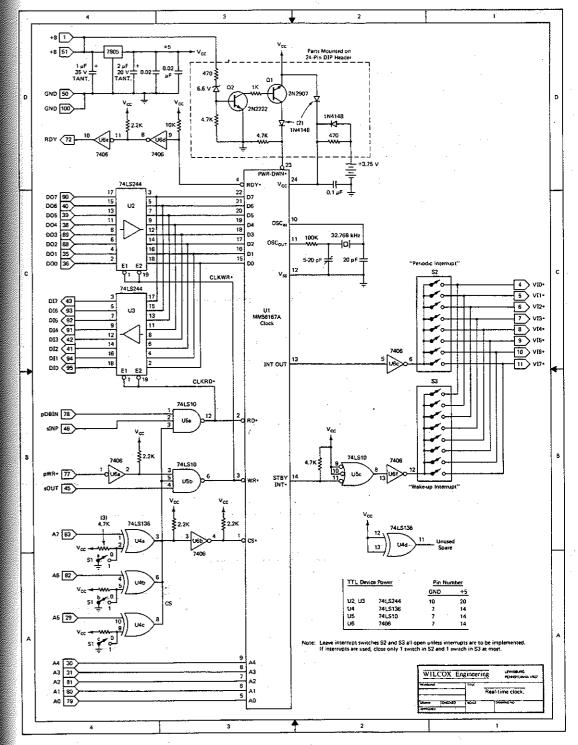

Figure 5.7 Real-time clock schematic drawn on zonal-coordinate paper.