Rickey's World www.rickeyworld.info

# An OrCAD Tutorial for ELEC 424 High-Speed Systems Design

Revision 1.0 - Spring 2002

## **An OrCAD Tutorial**

#### 1. Introduction

OrCAD is a suite of tools from Cadence for the design and layout of printed circuit boards (PCBs). We are currently using version 9.2 of the OrCAD suite. This document will give you a crash course in designing an entire circuit board from start to finish. This will be a very small and simple circuit, but it will demonstrate the major concepts and introduce the tools behind completing a PCB design. After you have completed this tutorial, you will know all the steps needed to make PCBs using OrCAD. This is not, however, a guide to the inner workings of the OrCAD interface. You should use this document in conjunction with the online OrCAD help and tutorials.

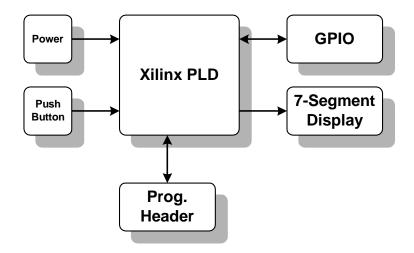

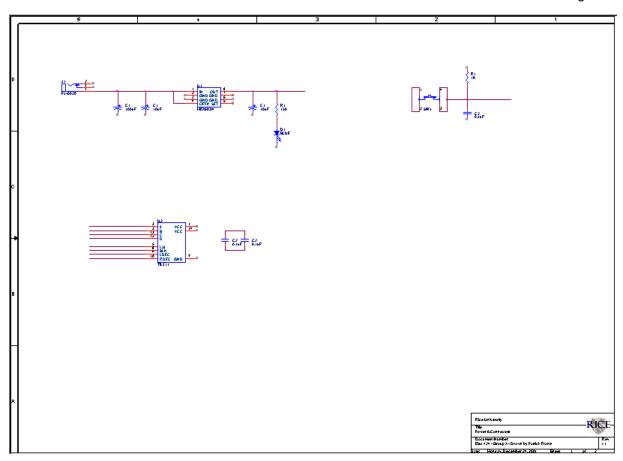

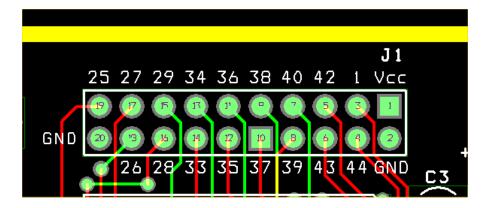

The circuit you will design is shown in the figure below. The main component is a programmable logic device (PLD) from Xilinx. PLDs, as the name implies, are programmable devices that can be used for a variety of useful tasks, and it is useful to be familiar with using them. In this circuit, we will use the PLD to light up a 7-segment LED display that will be used as a counter. Also in the circuit: a power connector for a 9-volt battery, a header for general purpose IO, a pushbutton switch, a programming interface for the PLD, and some miscellaneous resistors and capacitors.

OrCAD really consists of two tools. Capture is used for design entry in schematic form. You will probably be already familiar with looking at circuits in this form from working with other tools at Rice. Layout is a tool for designing the physical layout of components and circuits on a PCB. During the design process, you will move back and forth between these two tools.

Save your work frequently while working on this tutorial. You will not be reminded to do so.

## 2. Before You Begin

It is helpful to be very organized when you are designing. OrCAD will create many files and if you keep all of them in the same directory, it can quickly become very confusing. I like to make a directory hierarchy and put associated files into subdirectories. Before beginning, navigate to the directory in which you will keep your project and create the following subdirectories:

**sch** – for your schematics.

- lib for symbol and footprint libraries.

- **boar d** for your board files.

- **comps** for component datasheets.

- **assy** for assembly related documents.

For larger designs, more subdirectories would be desirable, but these will be sufficient for this project.

## 3. Starting a New Schematic Project

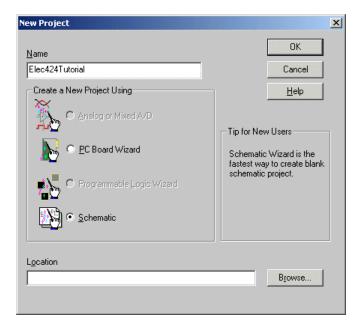

To create a new project, first start OrCAD Capture and click File-New-Project. You will see the following dialog box.

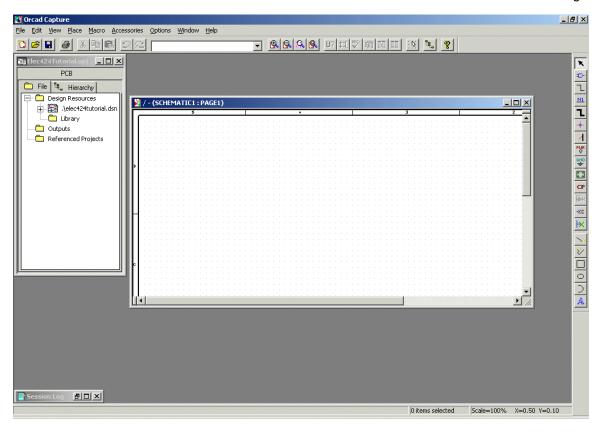

Browse to the **sch** directory that you created and name the project **Elec424Tutorial**. You now have an empty project workspace. You should see an empty schematic page and a project window like the following.

#### 4. Creating a Schematic Parts Library

OrCAD allows you to create a library of part symbols for use in schematic entry. These libraries are kept in separate files that are included in the project workspace. This allows you to reuse libraries in other designs. We will know create symbols for all the parts in our design.

IMPORTANT NOTE: When you place a part in a design, OrCAD creates a cached copy of the part symbol in the design file. This makes schematic projects portable but can also introduce some problems later in the design cycle. Please resist the temptation to edit parts directly in schematics, as this will make the design out of sync with respect to your library. Always edit symbols in the library and then use the Replace Cache and Update Cache commands to change the part in schematics. See the OrCAD help for more information on these commands.

First we must add a new library to our design. To do this, click File-New-Library. Your project window will now look like the figure on the left.

Right-click the library file and select Save As... Name the file Elec424Tutorial and place it in the | i b directory that you created earlier. You are now ready to add parts to your library.

## 5. Creating Schematic Symbols

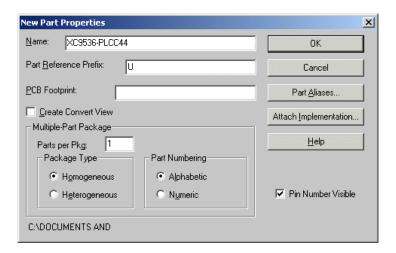

To add a new part to your library, right-click the library file and select New Part. This will bring up a dialog box for New Part Properties, which looks like this.

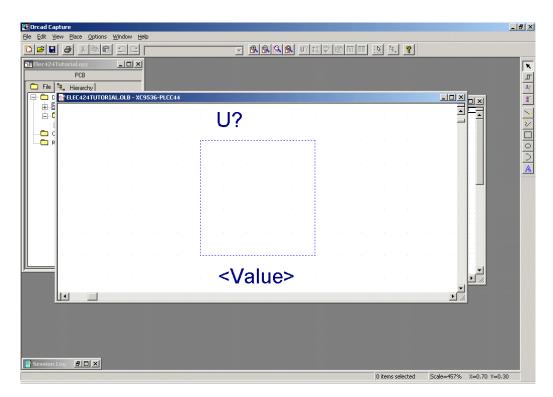

We will be making a symbol for the Xilinx XC9536 PLD. This part comes in a 44-pin PLCC package. Name the part **XC9536-PLCC44**. Leave the **Part Reference Prefix** as **U**<sup>1</sup>. You can leave the default values for all the other settings. Click **OK** to bring up the workspace for part creation. It should look like the picture below. Tools for working with the part are located on the toolbar on the right-hand side of the screen.

<sup>&</sup>lt;sup>1</sup> Part Reference Prefixes (also known as Reference Designators) help categorize parts in your schematics and PCB layouts. There is a pseudo-standard reference for most types of parts. For example, C is used for capacitors, R for resistors, L for inductors, U for ICs, and X for crystals.

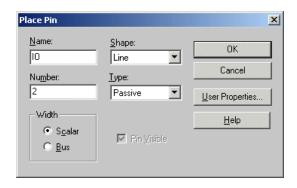

To get started, drag the dashed line on the workspace to make it a little larger. You won the able to fit too many pins on the part with its current size. When it is large enough, use the **Place**Rectangle tool to draw a solid outline in the same place as the dashed line. Use the **Place**Pin tool to place pins on the part. You will see a dialog that looks like this.

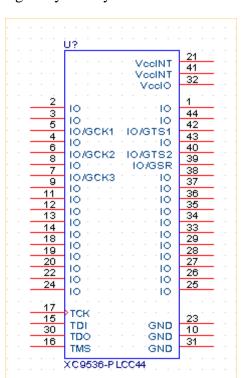

Refer to the part datasheet for the correct pin numbers for the PC44 package. You can either download the datasheet from the Xilinx web site (www.xilinx.com) or from Owlnet at the following location.

/ home/ j pf r ant z/ el ec424/ t ut or i al / comps/ XC9536. pdf

The default pin **Shape** (Line) and **Type** (Passive) are OK for most pin types. For clocks and active low signals you may want to use some of the other shapes. You will also want to use the type **Power** for

power pins. When you do this, make sure that the **Pin Visible** check box is checked. Also, I usually like to place my power pins near the top of the part and ground pins near the bottom. As a last touch, double-click the text that reads **<value>** and change it to read **XC9536-PLCC44**. When you are all done, your part should look something like the symbol on the left.

Save your part and close the window. You may get a warning about duplicate pin names, but that is OK to ignore. Your part will now be visible in your library.

Some parts are already in existing OrCAD libraries. It is usually OK to copy these parts for use in your own design. For example, let s say we want to use a sim ple resistor in our design. First, we need to open the library that contains the resistor. To do this, select File>Open>Library. OrCAD keeps all of its libraries in the path:

#### C: \ Program Files\ Or CAD\ Capture\ Li brary

Select the library called Discrete. This will open up a new window showing the contents of the library. Find the part called

R and highlight it. This is our resistor. Select **Edit Copy** from the menu and then highlight your own library. Select **Edit Paste** from the menu and this will paste the part into your library.

When you do this, some extra parts will show up in your library. These are part aliases (the same part but with a different name). You can tell the aliases by the ..., that is inside the little gate next to the part name. You don theed the aliases they will just cause confusion. Delete them from your library.

I have provided a library of the remaining parts for use in this design. Open this library file and copy the all the parts into your library. You can find this library on Owlnet at:

/ home/ j pf rant z/ el ec424/ t ut ori al / l i b/ t ut ori al . l i b

IMPORTANT NOTE: There are a few things to note about copying parts from existing libraries. First, always be sure to check the part you are copying against a datasheet for correct pinout, number of pins, etc. Second, some of the standard parts will have power pins that are invisible. Personally, I feel that this is a very bad design practice that can lead to errors in your design. If you copy a part that has invisible power pins, please be sure to make them visible. Trust me, this can save you a lot of pain and trouble later. Finally, beware of so-called "heterogeneous" parts. These parts split across multiple symbols. For example, you might see a part with general pins on one symbol and power pins on another. In general, heterogeneous parts should be avoided because they can cause problems. However, they may be acceptable for very large parts such as processors.

## 6. Schematic Entry

6.1 SETTING UP THE ENVIRONMENT - Now that you have your parts library set up, you are ready to begin entering schematics. You can see from the project window that you already have one page of schematics called **PAGE1** in a folder called **SCHEMATIC1**. If you can t see this, click on the ,,+ next to the dsn file to expand the view. Even though our circuit is small enough to fit on one page, we will use two pages to demonstrate a schematic with multiple pages. First add a new schematic page by rightclicking the schematic root folder and selecting **New Page**. You will be prompted to provide a name for this page. Call it Page 1 - Power & Connectors. Now rename the original page by right-clicking and selecting Rename. Call this Page 2 - Xilinx PLD. It is always nice to give your schematic pages useful names. While you are at it, rename the schematic folder in the same manner, calling it **Elec424Tutorial**.

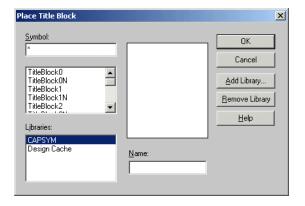

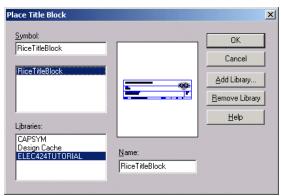

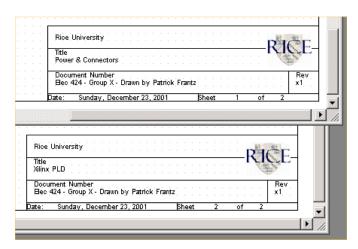

Open page 1 of your schematics by double-clicking it in the project window. This will bring up a blank page. B efore we place parts, let s do a couple of things. First, I like to make the page size a bit bigger than the default. You can fit a lot more onto the page and it will still look nice when printed. To do this select Options -> Schem atic Page Properties... Click the Custom radio button and use the following values (width=15.2, height=11.5). Second, there is a title block in the lower right corner. We are going to replace this with our own, so highlight the title block and delete it. We add a new title block by selecting Place Title B lock... You will see the following dialog box.

The title block is in your library, so we need to add that to the list of libraries. Click the Add Library button to browse to and select the library you created for the tutorial. Once you have added the library, you will be able to choose the RiceTitleBlock to add it to your design. Place the title block in the lower right corner of your schematic page. The title block has fields to put information for each page of schematics. Double-click the text to edit each field and change the information on each page so that it looks something like this.

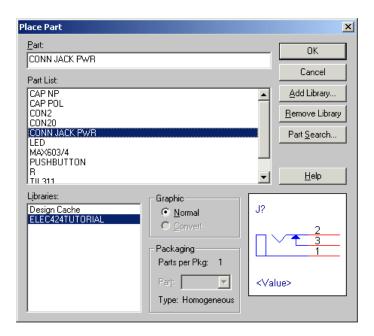

6.2 PLACING PARTS & MAKING CONNECTIONS - You are now ready to start placing the electrical components for your design. Open the first page of your schematics and click the Place Part icon on the toolbar on the right side of the screen. You will then get a dialog for choosing  $\rightarrow$ which part you want to place on your schematics.

Select the part CONN JACK PWR and click OK. Place the part on the left side of your schematic page. Now place the remaining parts on both pages using the attached completed schematics as a guide. A PDF file of the schematics can also be found on Owlnet.

/ home/ j pf rant z/ el ec424/t ut or i al / sch/ El ec424Tut or i al . pdf

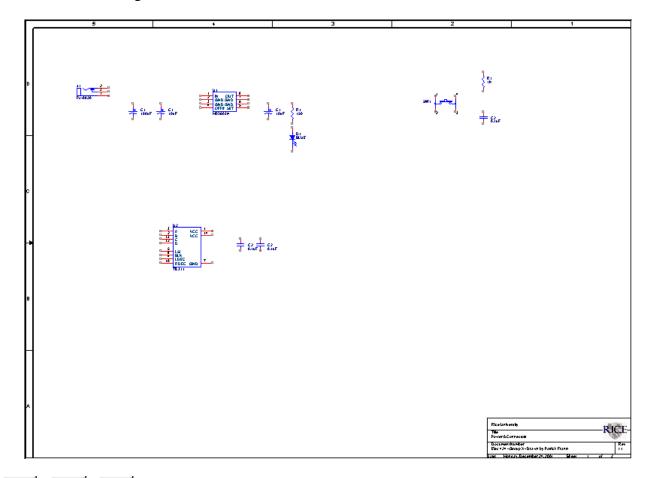

A small hint for moving around in 0 rC AD: use ,,I' and ,,O to zoom in and out, respectively. ,,C will center the design at your cursor. "R will rotate a part. You can do these actions while in the middle of another action (e.g. while placing a part). You will also notice that each part has a value associated with it. You can change this by double-clicking the current value. In this manner you can give all your capacitors, resistors, etc. the appropriate values. When you are done, the first page of your schematics should look something like this.

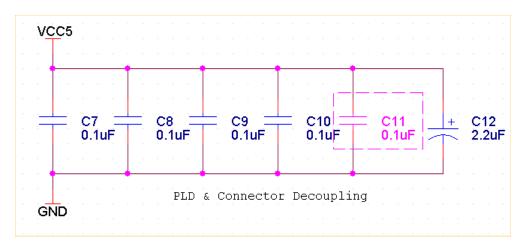

Now we need to draw nets to make electrical connections between components. To do this, click the Place Wire icon and connect the components as shown in the attached schematics. Use the Place Bus and Place Bus Entry icons to place busses and bus connections (you don t need to do this in these schematics). When you are done, the first page of your schematics should look like this.

Now you need to add power and ground connections to some of the parts. OrCAD has several built-in symbols for power and ground. I like to use a symbol that explicitly names the nets, as shown in the picture below. I do this because many designs will have multiple power and ground nets. Explicitly naming them helps prevent shorts and other errors. It also makes your schematics easier to read. Add power and ground to your schematics now.

6.3 CONNECTING PAGES AND NAMING NETS - Since some of these connections go to the PLD, we need to a way to connect the two schematic pages together. We can do this by using off-page connectors. To place these click the Place Off-Page Connector icon. Then select the connector called OFFPAGELEFT-L

or OFFPAGELEFT-R, it doesn't really matter which one, they are functionally the same. You can **≪**0 : place this on your schematic just like a part and then connect to it with a net. Off-page connectors are linked by a common name. For example, two off-page connectors on separate pages with the name CLK will be considered by OrCAD to be one net. To name a connector, just double click it to get a naming dialog box. Name your connectors now using the attached completed schematics as a guide.

**IMPORTANT NOTE:** For reasons that will become clear later, I like to place my off page connectors as close to the edge of the page (right or left) as possible. This makes clear which nets go off page and w hich don t. It will also help you find mistakes on naming nets across pages.

Normal nets can also be named. This is extremely useful and can help tremendously in the layout process. I encourage you to use the Place Net Alias icon to name any important nets such as clocks, address and data bus lines, and other specific signals you are interested in. To name a net, first highlight the net you want to name and then click the icon, you will be given a dialog box to

enter the name of the net. You can position the text anywhere you like. If you have already attached an off-page connector to a net, then that net already has the same name as the connector. You don theed to give the net an alias unless it will make your schematics more readable.

If you have any pins on parts that are left unconnected, use the Place No Connect icon to mark it in your schematics.

Now complete your schematics as shown in the attached reference.

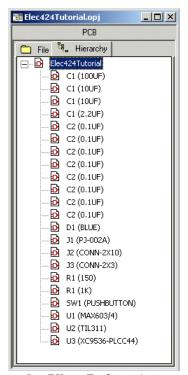

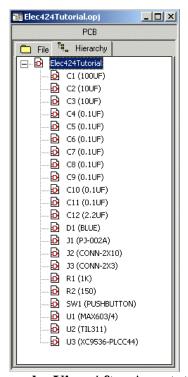

## 7. Preparing for Layout

7.1 ANNOTATION - Now that your schematics are complete, you are ready to prepare to export the design to Layout. From now on, you will be working in both Capture and Layout. The first step in preparing your design is to annotate it. Annotation really involves several steps. First, we will assign unique reference designators to all of the parts in our circuit. Remember reference designators? These are just labels that are used in Layout to uniquely identify different types of parts. If you look at the hierarchy view in the project window, you will see a jumble of reference designators. You might have several capacitors named C1 or a lot of parts that have the label, R?, C?, U?, etc.

**Hierarchy View Before Annotation**

**Hierarchy View After Annotation**

To fix this, we will use a few of the annotation tools. In the file view of the project explorer, highlight the top-level design file (the one with the dsn extension) and then select Tools-Annotate. You will see the Annotate dialog box.

In a new design, it is best to first reset all the part designators. To do this, click the radio button that says Reset Part References to "?" and then click OK. You will be asked if you want to save your design before proceeding. Every part in your design will now have a question mark in its reference designator instead of a number. Now, reopen the annotate dialog box and check the box that says Incremental Reference Update and click OK. This will go through your entire design and number each part starting with 1 for each part type. If you now look in the hierarchy view, you will see that you have a nicely ordered list of parts.

7.2 INTERSHEET REFERENCES - The next thing we will do is add intersheet references to your schematics. Doing this will place page numbers near each off-page connector that indicate to which other pages that net is connected. This is invaluable during design and debug because it will help you track individual nets across a large design in many pages of schematics. Since we only have two pages of schematics in this design, we could probably get away without adding intersheet references; however, it is a useful tool and should always be used for good design practice. Another reason for using this tool is that it helps to find mistakes in naming nets. For example, say you have a net named CLKIN but on one page of schematics you mislabel this net CLKIM. After annotation, these two off page connectors will not have page numbers next to them, indicating that they are single-pin nets. This would be an immediate warning flag that something is seriously wrong with your schematics. To add intersheet references, bring up the annotate dialog box again. Select the radio button that is labeled Add Intersheet References. You will get a secondary dialog box, and you can leave the default values as they are for now. Just click **OK** to continue. As far as schematics are concerned, your design is now fairly complete.

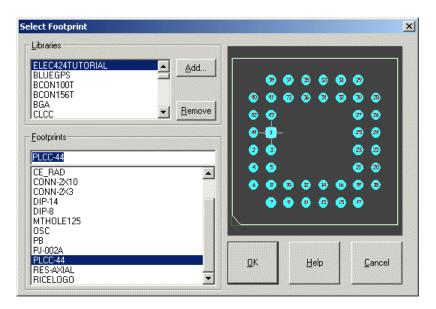

7.3 CREATING FOOTPRINT LIBRARIES – We are now ready to begin working in layout to proceed with our design. The first thing we need to do is create a library of footprints to be used in our PCB layout. Footprints<sup>2</sup> are a representation of the physical area that a part occupies on a PCB.

IMPORTANT NOTE: I cannot overemphasize this point. IT IS ABSOLUTELY CRUCIAL THAT YOUR FOOTPRINTS ARE CORRECT. Double-check them, triple-check them. It is sometimes possible to live with an error in a schematic symbol, but a footprint error can often sink your entire design. Please be **VERY CAREFUL**.

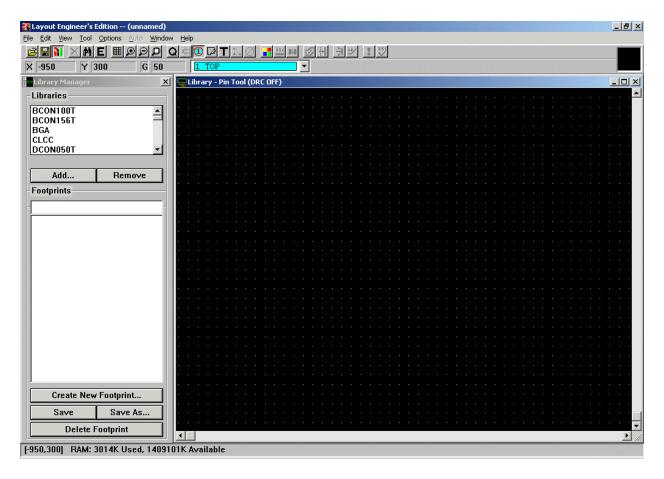

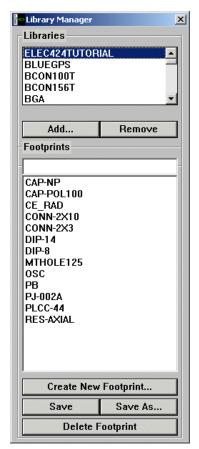

Start Layout Engineer's Edition<sup>3</sup> to begin working with footprints. Libraries for Footprints are very similar to libraries for schematic parts. Layout has a separate tool for working with footprint libraries, though. To start this tool, select Tools-Library Manager. You will get a new window that looks like this.

You will notice that there are already several libraries available for use. OrCAD has many existing footprints that you can use in your own design. As with the schematic symbols, be very careful to check that these footprints for correctness before using them. Often, you will have to make footprints for parts that don talready have one. Most datasheets for parts will contain the mechanical information necessary to make a correct footprint. However, before making a footprint it is necessary to understand a little bit about how PCBs are constructed.

<sup>&</sup>lt;sup>2</sup> Footprints are also sometimes referred to as shapes or land patterns.

<sup>&</sup>lt;sup>3</sup> There are two versions of Layout: Engineer's Edition and Plus. They are identical with the exception that Plus has an autorouter. We will not use this feature.

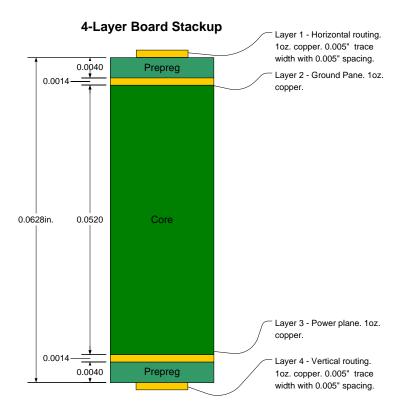

PCBs consist of a number of electrical and non-electrical layers. 2 to 4 electrical layers are fairly common for simple circuit boards. 8 to 20 layers can often be seen in many industry applications. The diagram below shows the electrical layer stackup for a 4-layer board like the one you are making now. The top and bottom layers are used for routing nets between parts, while the inner two layers are solid copper planes for connections to power and ground. A fiberglass or epoxy resin dielectric material separates each of the layers.

There are also several non-electrical layers:

- **Drill Layer** This layer defines finished drill sizes and drill locations for parts that have pins that go through the board. It is also used for general documentation.

- Solder Mask There is a coating on the top and bottom of the PCB that prevents solder from flowing freely on the board. This is what gives most circuit boards their green color.

- Solder Paste For parts that are "surface m ount (the pins rest on the surface of the board and do not go through it) this layer defines the spaces where solder (in a paste form) will be applied for circuit assembly. This layer is not used for manufacturing and is only used by the person assembling the board.

- Silkscreen This layer is used for documentation of a PCB. Reference designators and other

useful text can be printed on the top or bottom of a PCB using a process similar to that used for

silkscreen t-shirts.

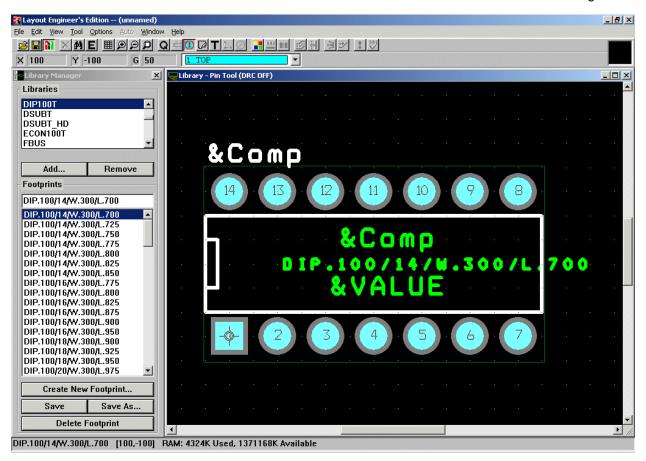

Footprints are composed of one or more padstacks. These padstacks define how a pin on a part looks on each of the electrical and non-electrical layers. Each of your footprints will need at least one padstack defined. Let s take a look at a padstack definition for an existing part. In the **Library Manager**, select the library **DIP100T** and highlight the first part **DIP.100/14/W.300/L.700**. You will see the part footprint in the **Library Manager**.

Layout uses a series of spreadsheets to store information about your design. Padstacks are stored in the padstack spreadsheet. To access this spreadsheet, click the View Spreadsheet icon and choose Padstacks. This footprint is composed of two padstacks, one for pin 1, which is square, and another padstack for the other pins. When you open the spreadsheet, you will first see a padstack called T1. Padstacks T1 to T7 are default padstacks and can be modified for your own use. The padstacks we want to look at are at the bottom of the list; scroll down until you see DIP100T.IIb pad1 or **DIP100T.IIb\_pad2**. These are the two padstacks for this footprint. You will notice that there are numbers on some of the layers that define how the padstack looks physically on that particular layer. We will come back to this in a minute.

Close the padstack spreadsheet and open up the footprints spreadsheet. The name is confusing; it should really be called something like the pins spreadsheet because this spreadsheet defines the locations of the pins and also which padstack they use. You will see each pin for the part in this spreadsheet, its x and y locations, and the padstack used for each pin. Notice that pin 1 uses the square padstack, while the others use the round one.

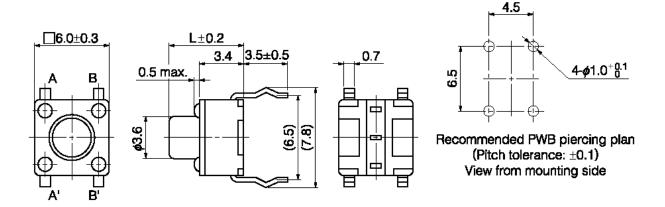

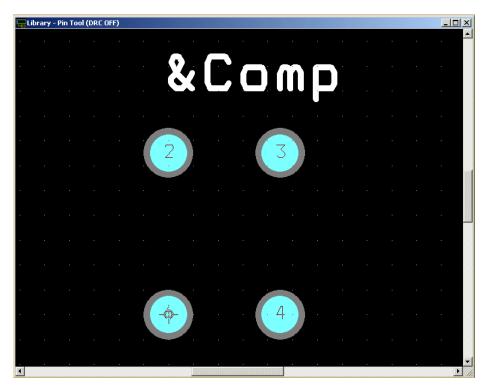

Now let's create a new footprint from scratch for your design. We will make the footprint for the pushbutton (Panasonic part EVQ-PAG04M). The mechanical diagram from the datasheet gives us all the information we need to know.

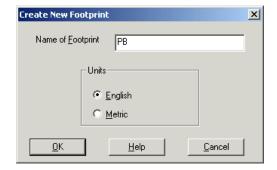

In the Library Manager, click Create New Footprint. This will bring up the following dialog box.

Name the footprint PB, and keep English for the Units. Even though the dimensions for the part are given in metric, most PCB fabrication measurements are still done in inches (or mils, 1/1000 of an inch). We can switch between the two systems fairly easily in OrCAD. Click OK to create the part. You will now see a new part with just one pin in the Library Manager.

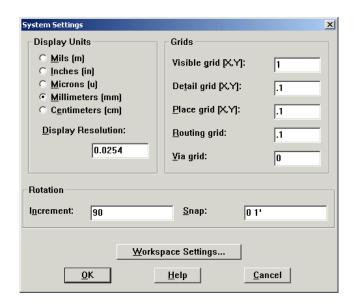

Since this is a metric part, we need to change the systems settings to use metric instead of English. Select Options-System Settings to bring up the following dialog. Change the systems settings as shown.

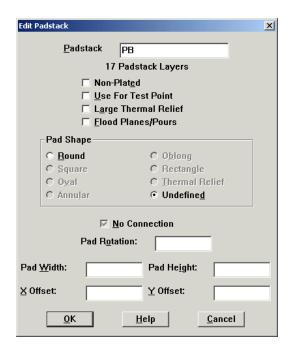

Click **OK** when you have made the changes. Now you are working in a metric system. The switch has 4 pins total, but we only need to define one padstack since the pins are all the same physically (not electrically). Open the padstacks spreadsheet. We will edit the padstack T1, which is already being used by pin1. First, let's start from scratch and fill in information for only the layers that we care about. In the spreadsheet, double-click the padstack name T1. This brings up the Edit Padstack dialog for all layers in the padstack.

First, change the name of the padstack to something more useful like **PB** (the name of our footprint). Doing this will make this padstack easier to find in Layout when there are 100s of padstacks to choose from. Next, select the **Undefined** radio button. This will reset the padstack definitions on every layer. Click **OK** to continue. In the spreadsheet you should now see a padstack called **PB** with no layers defined.

| Padstack or   | Pad       | Pad   | Pad    | X      |

|---------------|-----------|-------|--------|--------|

| Layer Name    | Shape     | Width | Height | Offset |

| PB            |           |       |        |        |

| TOP           | Undefined | 0.00  | 0.00   | 0.00   |

| воттом        | Undefined | 0.00  | 0.00   | 0.00   |

| PLANE         | Undefined | 0.00  | 0.00   | 0.00   |

| INNER         | Undefined | 0.00  | 0.00   | 0.00   |

| SMTOP         | Undefined | 0.00  | 0.00   | 0.00   |

| SMBOT         | Undefined | 0.00  | 0.00   | 0.00   |

| SPT0P         | Undefined | 0.00  | 0.00   | 0.00   |

| SPBOT         | Undefined | 0.00  | 0.00   | 0.00   |

| SSTOP         | Undefined | 0.00  | 0.00   | 0.00   |

| SSBOT         | Undefined | 0.00  | 0.00   | 0.00   |

| ASYTOP        | Undefined | 0.00  | 0.00   | 0.00   |

| ASYBOT        | Undefined | 0.00  | 0.00   | 0.00   |

| DRLDWG        | Undefined | 0.00  | 0.00   | 0.00   |

| DRILL         | Undefined | 0.00  | 0.00   | 0.00   |

| COMMENT LAYER | Undefined | 0.00  | 0.00   | 0.00   |

| SPARE2        | Undefined | 0.00  | 0.00   | 0.00   |

| SPARE3        | Undefined | 0.00  | 0.00   | 0.00   |

| T2            | i         | 1     |        |        |

We will now set each layer individually. You can also select multiple layers at a time by holding down the CTRL key when you click the layer name. First, let's define the size of the drill used for this part. The datasheet tells us that we need a drill of 1 mm for this part. Select the layers **DRLDWG** and **DRILL**. When you have multiple layers selected, you will need to right-click and choose Properties to bring up the Edit Padstack dialog. Choose the Round radio button and give the width and height a value of 1. Click **OK** when done. The changes you made should now be reflected in the spreadsheet.

Now we will define the amount of metal on the routing layers beyond the size of the drill. This is called the annular ring. Each board shop will have requirements on the minimum annular ring size based on the drill diameter. In most cases 20 mils (1 mil = 1/1000 inch) is a safe bet. 1 mm is approximately 40 mils, so 20 mils is about 0.5 mm. Select the following layers and bring up the Edit Padstack dialog: TOP, BOTTOM, INNER. Even though we have no inner routing layers, it is good practice to go ahead and define them. Make the pads round and put the value of 1.5 in the height and width fields.

Next, we need to define the clearance on the plane layers. The middle layers of our circuit board are solid pieces of copper that are used for power and ground. To prevent short circuits, we need to define a clearance around our drill. Most board houses will also have requirements for this, but 35 mils beyond the drill size is usually a good start. In our case, we will do a little rounding and just use 2 mm. Select the **PLANE** layer and define a round pad with a height and width of 2 mm.

The last thing we need to define is the solder mask. This is usually defined as slightly larger (about 5 mils) that then annular rings on the top and bottom layers. Select SMTOP and SMBOT and make them round pads with height and width of 1.625 mm.

You have finished defining your padstack for this part. You can close the spreadsheet and you will see that pin 1 should now look a little different based on the changes you just made.

You probably noticed that you don tneed to define all of the layers. As a guide, here are the layers that you need to define for thru-hole and surface mount parts.

- Thru-Hole TOP, BOTTOM, INNER, PLANE, SMTOP, SMBOT, DRLDWG, DRILL

- Surface Mount TOP, SMTOP, SPTOP

As far as padstacks are concerned, surface mount parts are a lot easier to work with.

Library Manager can be a bit flaky sometimes, so it is best to save your changes to footprints often. Go ahead and click Save As. You have not yet created a footprint library, so you will need to click the Create New Library button. Browse to your lib directory and name the library Elec424Tutorial.

Let s now clean up a few things before adding the rest of the pins. Y ou will see a lot of text on your screen. Most of it is on the layer ASSYTOP, which we will not use. This text is safe to delete. Open the text spreadsheet and you will see five text items. Select all the text on the ASSYTOP layer and delete them. This will clean up your footprint a bit. You can leave the reference designator text on the SSTOP layer. We will need it.

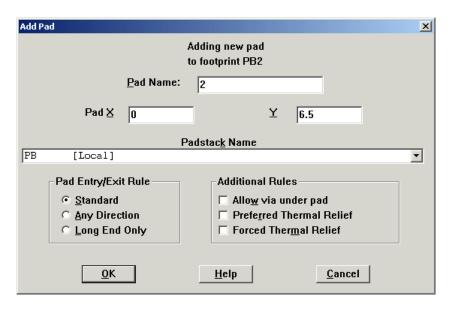

We can add pins to the footprint in a number of ways, but the easiest way to do this is to use the footprints spreadsheet. Open the spreadsheet and you will see just pin 1 with an x,y location of 0,0. **ALWAYS PLACE PIN 1 AT 0,0**. For this part we have to take note of a few things. Our schematic symbol has pins 1 to 4, while the datasheet for the part labels the pins A, A', B and B'. We will make pin 1 = A', pin 2 = A, pin 3 = B and pin 4 = B'. To create a new pin, just highlight pin 1 in the spreadsheet and type CTRL-C. This will create open the following Add Pad dialog.

This dialog allows you to give the pad a name (OrCAD autoincrements, so 2 is already given as the name), adjust the x and y coordinates of the pin, and choose which padstack you want to use for the pin. In most cases, you will leave the other settings as they are by default. Set the x and y coordinates as they are shown above and click **OK**. Add the remaining two pads as shown on the mechanical drawing for the pushbutton. When you close the footprint spreadsheet, your footprint should look like this.

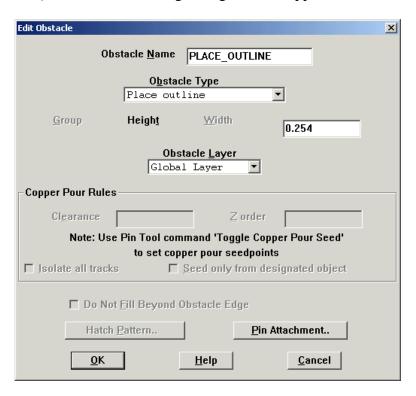

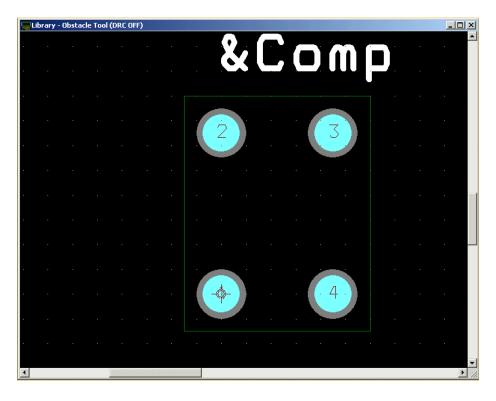

You are not quite done with the footprint even though all the pins are placed. There are just a few things left to do. First, we need to define a place outline. A place outline is a mechanical boundary that Layout uses to keep parts from hitting each other once assembled. In this case, the part outline is easy to draw. The physical switch does not extend beyond the square defined by the pads, so we will just draw a box around them. To do this we use the **Obstacle Tool**. Click the tool icon to switch to the obstacle tool and then right-click in the workspace. Select **New** from the context menu. Right-click again and select **Properties**. The following dialog box will appear.

Give the obstacle a meaningful name. Select **Place Outline** as the **Obstacle Type**. The width in this case is arbitrary. The layer is very important. This part is a thru-hole part, so in this case we want to make sure that surface mount parts on the bottom side of the board will not interfere with this part. By choosing **Global Layer**, the place outline will extend through every layer of the board. If this were a surface mount part, we could put the place outline on the top layer only. Click **OK** when you are done making changes. Now you need to draw the outline. Left-click to place each corner. When you have draw n at least 3 corners, you can press "**F** to have 0 rC A D finish the outline for you. It should look like this.

There is just one last thing you need to do to make your footprint complete. It is often nice to have an outline of the part on the silkscreen layer. This is not necessary, but it is a nice touch and makes things a bit easier during assembly of your board. We can easily make this outline by copying the place outline in the obstacles spreadsheet. Open the obstacle spreadsheet and copy the place outline by highlighting it and pressing CTRL-C just like you did for copying a pin. Double-click the new obstacle to bring up the Edit Obstacle dialog. Give the obstacle a meaningful new name, change the type to Detail, and change the layer to SSTOP.

Congratulations! You have created your first footprint.

I have provided a library of the remaining footprints for use in this design. Use the Add... button to add the library to the list of available libraries. Use the Save As button to copy each footprint into your own library. You can find this library on Owlnet at:

/ home/ j pf r ant z/ el ec424/ t ut or i al / l i b/ t ut or i al . l l b

Copy all of the parts from this library into your library.

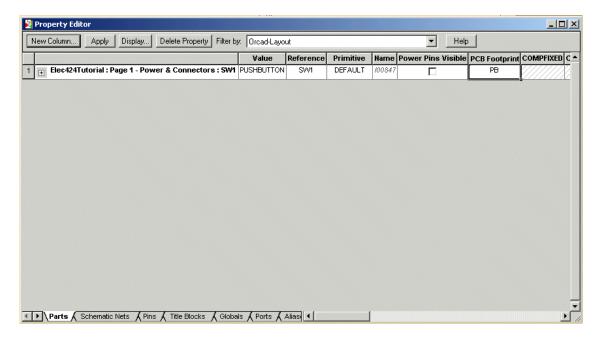

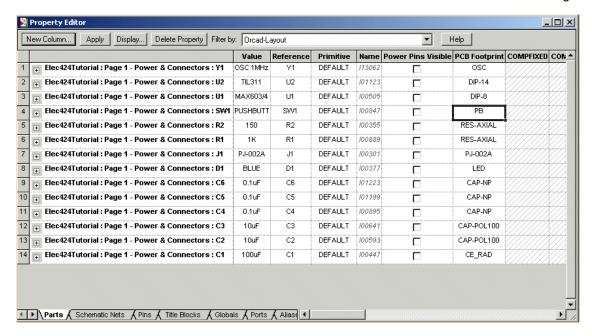

**7.4** ASSIGNING FOOTPRINTS TO PARTS – You will now switch back briefly to working in Capture. Open your tutorial schematics if they are not already open. You have defined a set of footprints to be used in your design, but now you must assign those footprints to each of the parts in your design. Each part in your schematics has a property called **PCB Footprint** and this must match one of the footprints in your footprint library. There are several ways to assign footprints to schematic symbols. One way is to open the **Property Editor** by double-clicking the part in schematics. This will show you all the properties for that part. Double click the pushbutton switch on the first page of your schematics. This is the part whose footprint you just drew.

There are quite a few properties, and it may seem a bit confusing. Using the drop-down list, you can filter by specific properties. Choosing **Orcad-Layout** will help make things make a little more sense. You should be able to see the **PCB Footprint** property now and assign it a value of **PB**, the name of the footprint you just drew.

Now imagine that you have hundreds of parts in your design. It could take quite a while to assign each footprint to every part. It would be much better if we could do it en masse. Fortunately, there are several methods we can use to do this. Close the property editor and press **CTRL-A** while on a page of schematics. This will highlight every part on the page. Press **CTRL-E** to bring up the **Property Editor**. Now you can see the properties for every part you have highlighted (make sure you are on the **Parts** tab of the spreadsheet because others are also visible). Now you can assign footprints to an entire page at once.

This is certainly an improvement. Now you can manipulate all the parts on one page. But what if you had 10 or more pages of schematics? This could still be cumbersome. In the next section, I will describe a much more powerful way of editing the properties in your design.

**7.5 IMPORTING AND EXPORTING PROPERTIES TO AND FROM SCHEMATICS** – As you may have noticed by now, OrCAD stores quite of number of properties in the design file. However, it can sometimes be cumbersome to manipulate these in OrCAD itself. Luckily, it is possible to export the properties of your entire design so that they can be edited in another program like Microsoft Excel. We will use this feature to assign footprints and other part information. After reading this section you may think that this is a lot of trouble to go through for this small amount of work. For this design, that may be the case. However, in much larger designs this is truly a timesaver.

To export properties highlight the top-level design file in the file view of the project explorer (the one with the dsn extension). Then select Tools->Export Properties... You will see the following dialog.

You can leave all the default selections. Just click **OK** to create the export file. It will be placed in the same directory as your schematic project and should have an **exp** extension. We can now edit this file

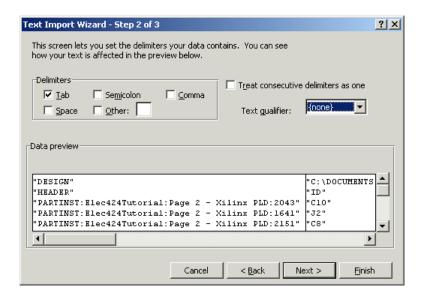

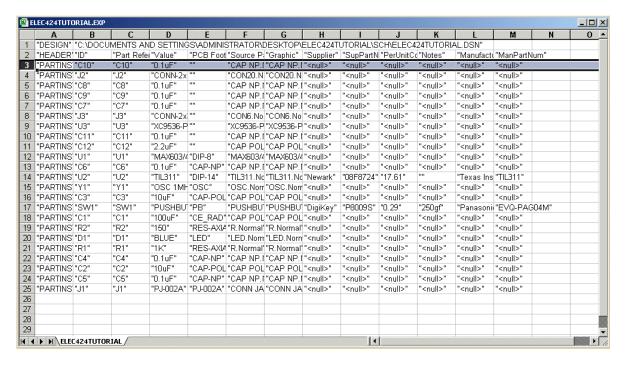

directly and re-import it into Capture. If you look at the file in a text editor like Notepad, you will see that it is just a tab-delim ited file with the values enclosed in quotation marks. Let sopen this file with Microsoft Excel so we can manipulate it better.

Start Excel and select File >0 pen... Browse to where your file is located. You will probably have to change the file type to All Types (\*.\*) to see the file. Selecting the file will start the Text Import Wizard.

Click the **Next** button on the first screen. On the second screen, it is important to change the text qualifier to {none}. This will preserve the quotes around the values. If you do not do this, then you will be unable to re-import the file back into OrCAD. When you have made this change you can go ahead and click Finish. You will now have the data in Excel. Let s do a few things to make moving around a little easier. First, I like to freeze the top two rows so that they are always visible. This way I can always see what the name of each column is. To do this, click row 3 to highlight the entire row. Then select Window→Freeze Panes.

Next, I like to sort the spreadsheet so that it makes a little more sense. Highlight all of the rows and columns of your spreadsheet except the first row. Then select Data → Sort... to bring up the Sort dialog.

I like to sort by Value and then by Part Reference. Once this is done, your parts should all be grouped by common value. For example, all of your 0.1uF capacitors should be next to each other. This will make it much easier to assign footprints and other properties to similar parts.

**IMPORTANT NOTE:** It is crucial that parts with the same value all have the same text in their value fields. For example, you may know that .1uf and 0.1uF are the same thing, but OrCAD treats that as two separate values and will think that the two are completely different parts. This will complicate parts ordering and make your BOM (parts list) unreadable. If you find discrepancies like this, you can fix it in Excel or in OrCAD.

Fill in the remaining footprints based on the chart below. The reference designators in your schematics may vary slightly from those in the table, but this will make no difference to the design. Two things are important when you are assigning the footprints. First, make sure that you enclose the value in quotation marks or the im port back into 0 rC A D won twork. Second, make sure that the

footprint name matches exactly the name that you gave your footprint in your library. If the name does not match, then you will get errors when you export your design to Layout.

| "Part Reference" "C10" | "0.1uF"                     | "PCB Footprint" "CAP-NP"  |

|------------------------|-----------------------------|---------------------------|

| "C11"<br>"C4"          | "0.1uF"<br>"0.1uF"          | "CAP-NP" "CAP-NP"         |

| "C5"<br>"C6"           | "0.1uF"<br>"0.1uF"          | "CAP-NP" "CAP-NP"         |

| "C7"<br>"C8"           | "0.1uF"<br>"0.1uF"          | "CAP-NP" "CAP-NP"         |

| "C9"<br>"C1"           | "0.1uF"<br>"100uF"          | "CAP-NP" "CE_RAD"         |

| "C2"<br>"C3"           | "10uF"<br>"10uF"            | "CAP-POL100" "CAP-POL100" |

| "R2"<br>"R1"           | "150"<br>"1K"               | "RES-AXIAL" "RES-AXIAL"   |

| "C12"<br>"D1"          | "2.2uF" "BLUE"              | "CAP-POL100" "LED"        |

| "J2"<br>"J3"           | "CONN-2x10" "CONN-2x3"      | "CONN-2x10" "CONN-2x3"    |

| "U1"<br>"Y1"           | "MAX603/4" "OSC 1MHz"       | "DIP-8" "OSC"             |

| "J1"<br>"SW1"          | "PJ-002A" "PUSHBUTTON"      | "PJ-002A" "PB"            |

| "U2"<br>"U3"           | "TIL311"<br>"XC9536-PLCC44" | "DIP-14"<br>"PLCC-44"     |

Save the file in Excel. You will get several warnings about the incompatibility of the format. You can just ignore these. There is one small last step that we need to do before we can import back into OrCAD. Excel will replace one set of double quotes with three, so we need to open the file in a text editor. Use Notepad or another text editor to open the file and do a search and replace to change """ with ". Save the file when you are done.

Now you can import the properties file back into OrCAD. In Capture, highlight the design file in the file view of the project explorer. Select Tools > In port Properties... Browse to your properties file and click OK. You should not get any errors during the import. If you do, then there is likely a wrong footprint name or some missing quotation marks in the file. You will need to correct this before proceeding.

7.6 EMBEDDING THE BOM IN SCHEMATICS – You may have noticed in Excel that some parts had some extra information. OrCAD is a great place to store information about where parts are bought, who makes them, how much they cost, etc. If all the information is there, then OrCAD can use the information to automatically generate the BOM (Bill of Materials). The BOM will help you be organized when ordering parts, and it is essential for the person assembling your board. There are several extra fields that you probably saw with this kind of information.

- **Description** A description of the part. Usually I cut and paste this from the description of the part from the supplier s web page (e.g. D ig i-Key).

- ManPartNum The m anufacturer spart num ber.

- **Manufacturer** The manufacturer of the part.

- Notes Any miscellaneous information about the part that you want to record. Maybe it has a long lead-time and you want to note that.

- **PerUnitCost** How much each part costs.

- SupPartNum The supplier s part num ber (e.g. D ig i-Key, Arrow, Newark, etc.).

- **Supplier** The supplier of the part.

Export the properties of your design again and fill in the information for each part. To help you, I have put an Excel version of the BOM in the following location on Owlnet.

/ home/j pfrantz/elec424/tutorial/assy/BOM xls

When you have finished editing the properties, save the file and import them into Capture just like you did for the footprints.

Now you are ready to have OrCAD generate a BOM for you. To do this, highlight the design file in the file view of the project explorer. Select Tools > Bill of Materials... to bring up the Bill of Materials dialog.

You will want to change a few of the default settings. Cut and paste the following text into the **Header** and **Combined Property String** fields of the dialog box.

Item\tQuantity\tReference\tPart\tDescription\tSupplier\tSupPartNum\t

Manufacturer\tManPartNum\tUnitCost\tNotes

{Item}\t{Quantity}\t{Reference}\t{Value}\t{Description}\t{Supplier}\

t{SupPartNum}\t{Manufacturer}\t{ManPartNum}\t{PerUnitCost}\t{Notes}

Then click **OK** to generate the file. This should put a file called **Elec424Tutorial.bom** in your **sch** directory. This will be a tab-delimited file just like when you exported the design properties. You can use Excel or another program to make it look a little more readable. Do this and put the finished version into the **assy** directory. This is one of the files that you will give to the assembler when you are ready to have your boards assembled.

7.7 CREATING A BOARD TEMPLATE FILE – You are almost ready to export your schematic design to Layout. Before doing this, we must create a board template file. This file defines some default properties for the board that will be used throughout layout. To create a template, start Layout and select File->New. When you see the dialog, press Cancel. You should now see a blank workspace. You can use the same shortcut keys that you used in Capture to zoom and center the design ("I, "O, and "C).

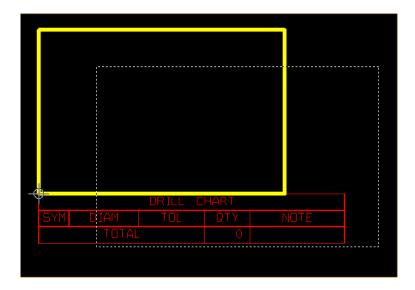

The first thing we need to do is draw a board outline to define the perimeter of the board. For this PCB, we will make the board 3 inches by 2 inches. The board outline is an obstacle like the ones you placed in the footprint editor. To create the board outline, select the **Obstacle Tool**, right-click and choose **New**... and then right-click again and select **Properties**... Name the obstacle **BOARD\_OUTLINE**, its type should be **Board Outline**, its **Width** should be 50 (mils) and it should be placed on the **Global Layer**. Place the first corner of the board at 0,0 and then draw from there. While drawing, you can use the information in the status bar to tell you where in the workspace you are. When finished, your board outline should look like this.

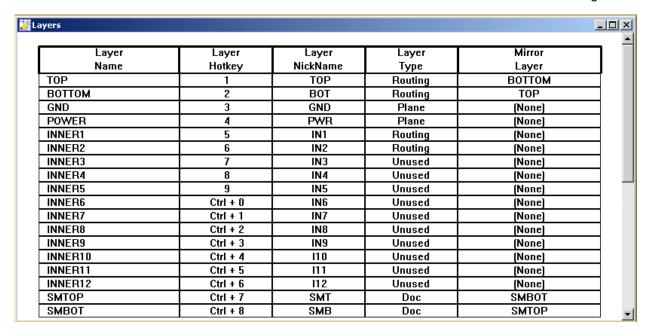

Next, you will edit the layer stackup. Layout has spreadsheets just like the **Library Manager** does. Click the **View Spreadsheet** icon and select **Layers**. This spreadsheet defines all the layers that your board uses and their respective functions in the design. You will see a spreadsheet that looks something like this.

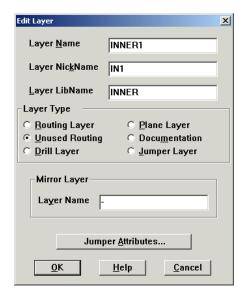

You are making a 4-layer board, so we will turn off some of the pre-defined layers because we will not use them. Double-click the INNER1 layer to bring up the Edit Layer dialog.

Select the Radio button for **Unused Routing**. Click **OK** to continue. Do the same thing for the following layers: INNER2, SPTOP, SPBOT, SSBOT, FABDWG, NOTES. Remember that you can use the CTRL key to select multiple layers at one time. Also remember that all designs are different and may need extra layers. For example, a design with surface mount components will need the SPTOP and SPBOT layers. If we were to place components on the bottom side of the board, then we would likely need a silkscreen on the bottom and, therefore, the SSBOT layer. Close the spreadsheet when you have made the changes.

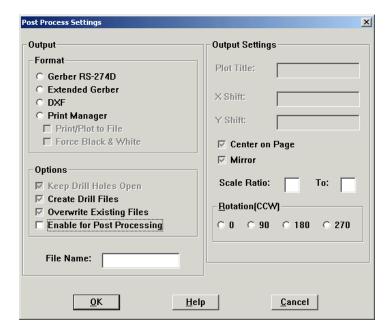

The next thing we need to do is change the output settings for the Gerber files<sup>4</sup>. Select **Options→Post** Process Settings... to bring up the Post Process Spreadsheet. Select the \*.ASB and \*.FAB lavers. Rightclick and select Properties to bring up the Post Process Settings dialog. Uncheck the box that is labeled **Enable for Post Processing**.

Now select all the layers. You can do this by clicking in the cell in the top-left corner of the spreadsheet (Plot Output File Name). Right-click and select Properties to bring up the Post Process Settings dialog. Select the radio button for Extended Gerber. This is the format we want to use for fabrication. Close the spreadsheet when you are done.

Next, you will define a default via<sup>5</sup> size. Click the View Spreadsheet icon and select Padstacks. This will open the padstacks spreadsheet and shows every padstack that is used in your design. Since there are no parts in the design right now, there are not that many padstacks, but this will change after we import from Capture.

You will edit the VIA1 padstack that is first on the list. This will become the default via for your design. Editing padstacks here is identical to how you edited padstacks when creating a footprint. Let's start with a clean padstack. Click the name VIA1 to highlight the entire padstack. Right-click and select Properties to show the Edit Padstack dialog. Select the radio button labeled Undefined and also check the box labeled Flood Planes/Pours. Click OK when done. This will reset the definitions for all layers of VIA1. Now you will set the finished drill size. Highlight the DRILL and DRLDWG layers and open the Edit Padstack dialog. Select a pad shape of Round and give it a width and height of 13.5 (mils). We are using the same clearance requirements that we used before when defining footprints: +20 mils annular ring, +25 mils solder mask, and +35 mils plane clearance. Select the **TOP**, **BOTTOM** and **INNER** layers (we have no inner layers in this design, but it is good practice to define this since we may want to add layers later in a design). Make these layers round with a diameter of 35 mils. Select the GND and

<sup>&</sup>lt;sup>4</sup> Gerber files are in a special format that the board house can read. These are the files used to generate film and fabricate your board. There is one file per layer of your design.

Vias are used to connect traces between layers and to make connections to solid ground or power planes.

**POWER** layers and make these round with a diameter of 50. Finally, highlight the **SMTOP** and **SMBOT** layers and make these round with a diameter of 40.

We will only use one via type in our design, but OrCAD will allow you to define up to 16 different vias. You might want more than one if you wanted slightly larger vias for carrying high-currents. You can even assign specific vias to specific nets, but that is beyond the scope of this tutorial.

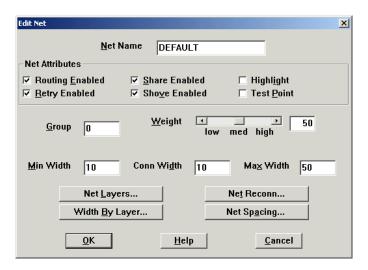

When a netlist from Capture is imported, we can set the default widths and other properties for all nets that get imported. After importing we can customize these parameters on a per-net basis. Let s set the values for the default net. Click the **View Spreadsheet** icon and choose **Nets**. You will see a spreadsheet with just one net, **DEFAULT**. After you import your netlist from Capture, you will see all the nets in your design in this spreadsheet. Double-click the net to bring up the **Edit Net** dialog.

Our design will not be too aggressive, so we will use 10 mil traces. Set the **Min Width** and **Conn Width** to 10, and set the **Max Width** to 50. Click **OK** when you have made the changes.

The final thing we need to do to our template is set a few global spacing constraints. These spacing values will be used when you have Layout automatically check for design errors. Select Options >G bbal Spacing... to bring up the Route Spacing spreadsheet. Click on Layer Name to highlight every cell, and then right-click and select Properties to bring up the Edit Spacing dialog. Put a value of 10 in every field and click OK. Close the Route Spacing spreadsheet.

Save your template. You are done with it and are ready to export your design from Capture to Layout.

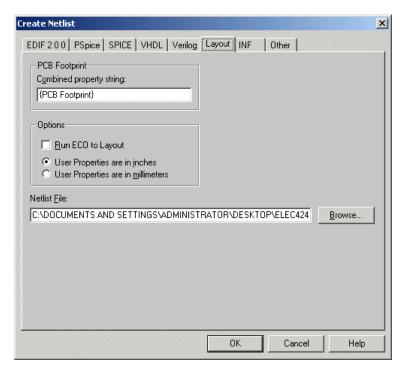

7.8 CREATING THE NETLIST – To export your design to Layout, you must first create a netlist. A netlist is a file that has all the parts, footprints and nets for your design in a format that can be read by the layout program. To start netlist generation, highlight your dsn file and select Tools→Create Netlist... to bring up the Create Netlist dialog box.

Click on the **Layout** tab in the dialog box. You don't need to modify any settings, just click **OK** to generate the netlist. When finished you should have a file called **Elec424Tutorial.mnl** in your **sch** directory. Your design is finally ready for import into layout.

## 8. Starting Layout

**8.1** CREATING A NEW BOARD — You have everything that you need to import your design into Layout. We need to do one thing before we begin. Layout will try to match the names of the footprints in your netlist with those stored in the **Library Manager**. Your library must be at the top of the list in **Library Manager** or the import will not work. Open **Library Manager** and make sure that your library appears at the top of the list like in the figure below.

Now start Layout and select File-New. You will first be prompted for the template file you created. It should be located in your board directory. Second, you will be asked for your netlist. This should be located in your sch directory. Third, you will be asked to give your board file a name. Name this file Elec424Tutorial and place it in the board directory.

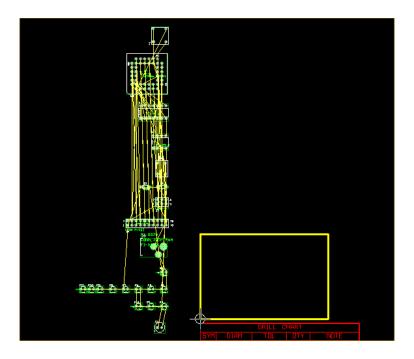

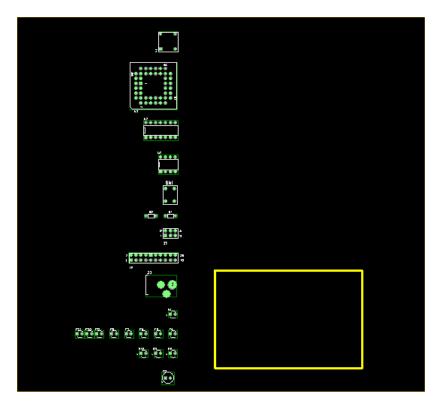

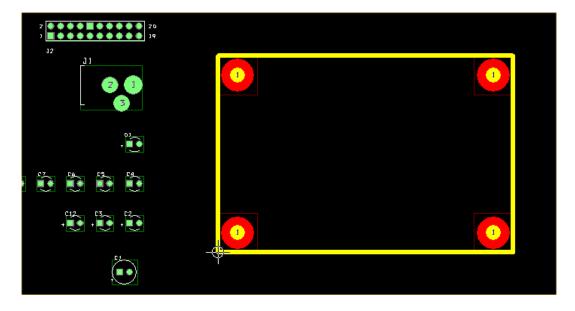

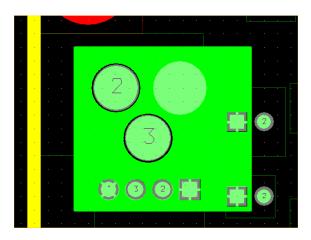

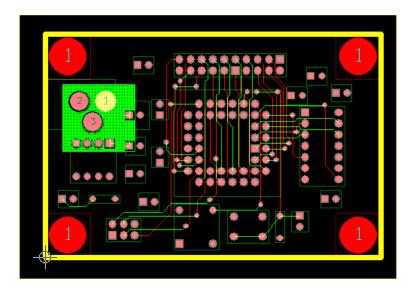

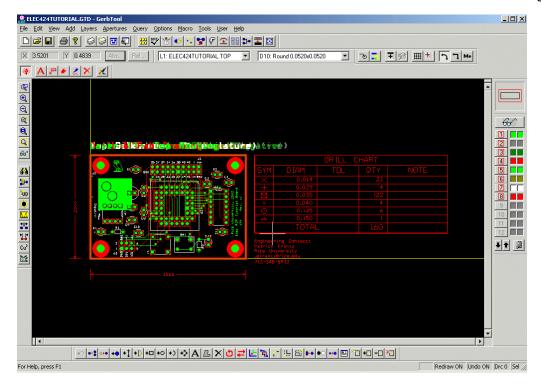

If all the footprint names in your design match those in your library, then you should get no errors and you will see a screen in layout like the one below.

If you got one or more errors, then it probably means that you have a misspelled footprint name. Sometimes, you can also accidentally assign a footprint that doesn thave the same number of pins as your schematic

symbol. If your import is unable to complete, then you will have to find the problem and start the process again.

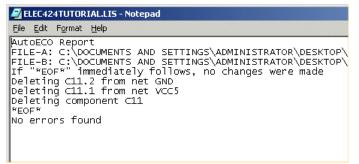

One useful tool for finding an error is the **lis** file. When Layout performed the import, it generated a file called Elec424Tutorial.lis in your board directory. Open this file in a text editor like Notepad to see what it looks like. This file will tell you everything that occurred during the import: what footprints were added or deleted, what components were added or deleted, and what nets were added or deleted (you will see later how footprints, components and nets get deleted). If an error occurred, you will see it here, probably towards the end of the file.

8.2 GETTING AROUND & PLACING PARTS – All of your parts from schematics should be line up on the left side of the board. Before we start placing them, let s do a few things to make our job a little easier. First, turn off DRC (Design Rule Checking). We will use it later when routing, but not now. DRC When you do this, the box with the dashed line border will disappear. Second, I like to turn off a few layers at this point, just to make the screen a little easier to look at. You will notice a drop down box with the **TOP** layer listed. This box lets you select the active layer<sup>6</sup>.

While a layer is active, you can press the ,-, key to make it visible or invisible. Try it now for the top layer. Your screen should look a little different, and the coloring in the drop down box will change to indicate that the layer is now invisible.

<sup>&</sup>lt;sup>6</sup> Layout has many shortcut keys to help you move around the program. They are extremely useful, and I encourage you to be familiar with them. For a complete description, search the help file for keyboard shortcuts.

Make the top layer visible again. You will want to see that one while placing parts and routing. For now, select the following layers and make them invisible: SMTOP, SMBOT, AST, ASB, DRD, DRL. You will also notice that there are a bunch of lines connecting your parts. These are connections that are still unrouted, and this is usually referred to as the ratsnest. When placing parts, it is sometimes useful to turn this off. So click the View Spreadsheet icon and select Nets. Remember when you used this spreadsheet before? It had just one net called **DEFAULT**. Now, every net in your design should appear in this spreadsheet. This spreadsheet can be a useful way to see if you have misnamed nets in your schematics. Highlight every net by clicking the cell labeled Net Name. Right-click and choose **Properties.** Uncheck the **Routing Enabled** box and click **OK**. The ratsnest should have disappeared.

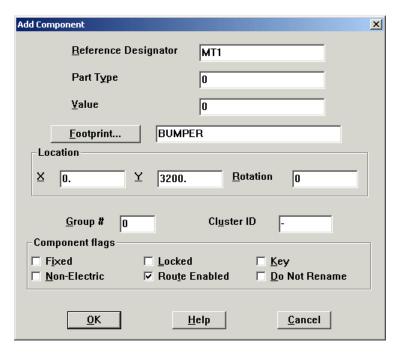

You are now ready to place parts on your design. To get into parts placement mode, make sure that the Component Tool is selected. In addition to placing the components that are in your schematics, you can also place non-electrical components right in Layout. You will do that now to place some mounting holes on your board. While using the Component Tool, right-click and select New to bring up the Add Component dialog box.

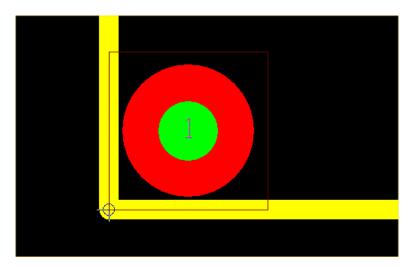

Give this component a reference designator of MT1. Then click the Footprint button and select the BUMPER footprint from your library. Click OK when finished. The part will now be attached to your cursor and you can place it on the board. We actually want to place this mounting hole so that the large pad is on the bottom of the board. Press "T to flip the part to the other side of the board, and then place at the edge of the board in the lower left corner.

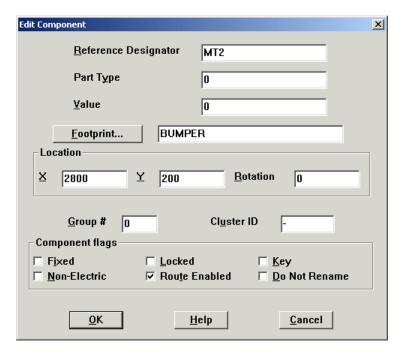

We want to place a mounting hole in each corner of the board. You could go through the procedure that you just did to place this component, but there is an easier way that will also allow you to precisely place components. Click the View Spreadsheet icon and choose Components to open the components spreadsheet. Scroll down until you see the component you just placed, MT1. Like in other spreadsheets, you can press CTRL-C to make a copy of the component. Do this 3 times to make components MT2 to MT4. When you copy the component, it will be placed at 0,0, all three need to be moved. Double-click MT2 to bring up the Edit Component dialog box.

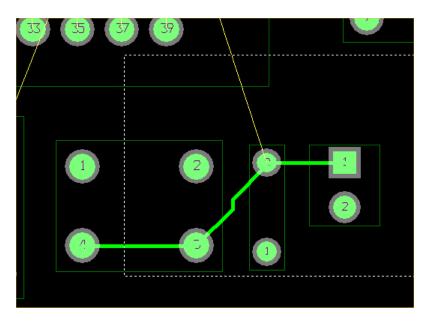

Change the coordinates for this part to 2800,200 and click **OK**. Now do the same for the other two parts and place them each 200 mils from the corners of the board. Before closing the spreadsheet, highlight all four parts using the **CTRL** key. Right-click and select **Properties** to bring up the **Edit Component** dialog again. Since these are non-electric parts, uncheck the box labeled **Non-Electric**. Also, we don t want to accidentally move the part, so check the box labeled **Fixed** and the box labeled **Locked**. Finally, uncheck the box labeled **Route Enabled**. Click **OK** to close the dialog and then close the spreadsheet. Your board should now look like this.

Now you can begin to place the rest of your components. You will probably want to print out your schematics so that you can see where the components are supposed to go in relation to each other. When you pick up a component, the ratsnest for that component will appear to show you the connections to other parts. If you want, you can also turn the ratsnest back on to see all of the connections. Personally, I like to turn on at least the power and ground nets and give them a distinct color, especially in designs with multiple voltages. Open the nets spreadsheet and find the net **GND**.

Right-click and select Change Color. Choose any color you like. Right-click again and select Enable <-> Disable. When you close the spreadsheet, the GND net should be visible. Do the same thing for the other power nets. When you close the spreadsheet it will look a little messy. You can use the **Refresh All** icon to force OrCAD to redraw connections.

When placing components, you may want to work on a finer grid. Right now, the grid is probably set at 100 mils. You can change this by selecting Options-System Settings and then changing the Place Grid setting. I usually use a value of 25. I also like to adjust the Visible Grid setting to give me an onscreen reference. I usually use a value of 50 when placing components.

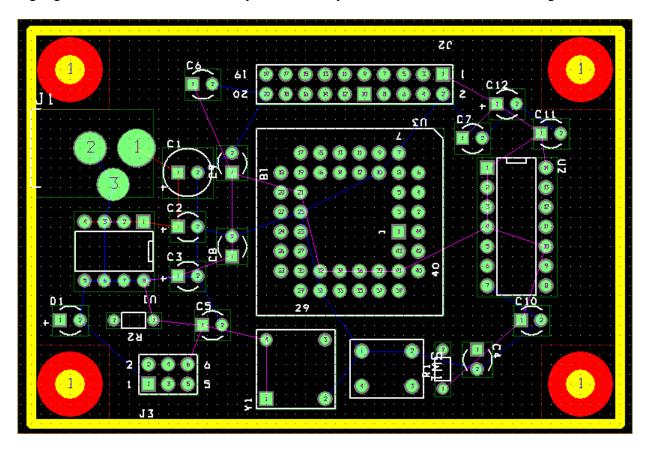

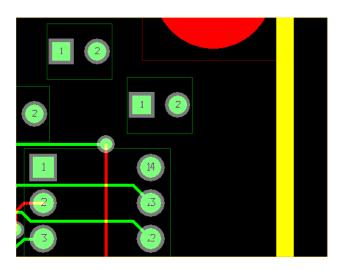

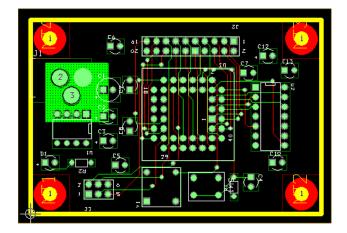

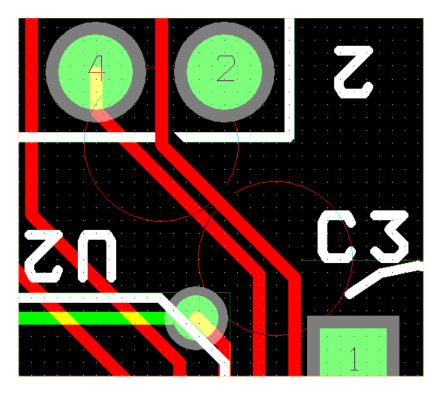

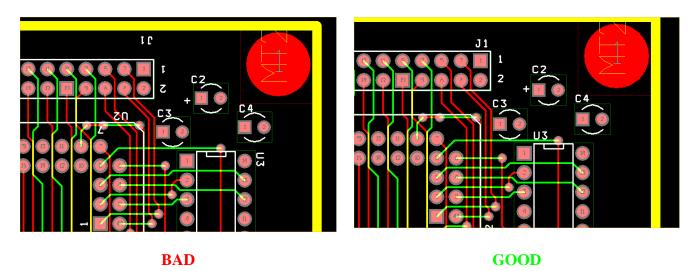

Start placing the remaining components on your board. Start with placing the power connector on the left side of the board, the PLD in the center, and TIL311 on the right. Try to keep components that belong together near each other. When you are done, your board should look something like this.

The silkscreen is a bit messy, but we will deal with that later. In fact, during routing, the silkscreen can get in the way, so go ahead and turn off the SST layer now using the same method you used before for the other layers.

Save your design. We have added a few components, so you may get the following warning.

We will address this later. Do not worry about it now.

**IMPORTANT NOTE:** Or CAD has a method to allow you to change your schematics while in Layout and to also make changes in Layout that will get sent back to Capture. Because of this, do not change your schematics until you are ready to re-export your design to Layout. If you make changes to both the schematics and the board layout at the same time, you will only make it difficult to reconcile the two.

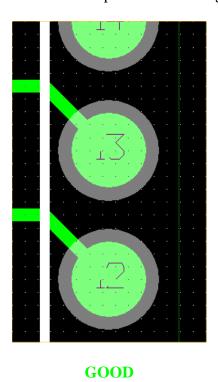

8.3 ROUTING POWER, GROUND AND COPPER POURS — In any design, it is usually wise to route all power and ground connections before anything else. On a thru-hole technology board, this is very easy because connections can be made to the solid plane as the pin passes through the board. The pin will be "flashed" to pow er or ground. We need to set up our design so that 0 rC A D knows that the two planes are associated with nets. Open the nets spreadsheet and find the net GND. Double-click to open the Edit Net dialog and click the button labeled Net Layers... Under the section Plane Layers, check the box labeled GND. This will inform OrCAD that the net GND is associated with the solid plane on layer 2. Do the same thing for the net VCC5. When you close the spreadsheet, click the Refresh All button. The ratsnests for VCC5 and GND will disappear. This is because they are now connected to the plane layer. To see this, press Backspace to clear the screen, then press "3" (the shortcut key for the ground layer) to view the ground layer.

You can now see all of the connections to the ground plane. You can do the same thing for the power plane. Press "F5 or the Refresh All button to make the whole design visible again.

We still have one voltage net to route, and that is the input voltage from an external power supply. This net only touches a few components, so we could just put a trace to connect all the components. However, we can also draw a solid piece of copper and associate it with that net. This is especially useful for high-current traces or small voltage planes. We do this using the **Obstacle Tool** just like

when drawing obstacles for footprints. Turn the **Obstacle Tool** on and then right-click anywhere in your design. Select New... and then right-click again and select Properties... to bring up the Edit Obstacle dialog. Name this obstacle VCC\_IN, leave the Width at 10 mils. Set the Clearance to 15 mils Change the Obstacle Type to Copper pour. Finally, set the Net Attachment to the name of the net, which should be V\_IN. Click OK and you are ready to draw your copper pour. Draw a rectangle around the power connector and other components that are attached to this net. When you are done, click **Refresh All** to redraw the ratsnests.

You have now routed all the power and ground connections. That was easy, right? Let s look a little bit at some of the tools that OrCAD gives you to check on the progress of your design. Click the View Spreadsheets icon and choose Statistics. The statistics spreadsheet gives you information on time in layout, percent of components placed, percent of traces routed, and some other information.

| Statistic          | Enabled | Total   |

|--------------------|---------|---------|

| Board Area         | 6.0     | 6.0     |

| Equivalent IC's    | 9.1     | 9.1     |

| Sq. inches per IC  | 0.66    | 0.66    |

| # of pins          | 137     | 137     |

| Layers             | 2       | 28      |

| Design Rule Errors | 0       | 0       |

| Time Used          | 7:10    | 7:10    |

|                    |         |         |

| % Placed           | 100.00% | 100.00% |

| Placed             | 27      | 27      |

| Off board          | 0       | 0       |

| Unplaced           | 0       | 0       |

| Clustered          | 0       | 0       |

|                    |         |         |

| Routed             | 55      | 55      |

| % Routed           | 100.00% | 62.50%  |

| Unrouted           | 0       | 33      |

| % Unrouted         | 0.00%   | 37.50%  |

| Partials           | 0       | 0       |

| % Partials         | 0.00%   | 0.00%   |

100% of your components should be placed, and you can also see that a majority of your traces have been routed (power and ground make up the majority of connections in most designs). You are well on your way to completing your design.

**8.4 ROUTING OTHER NETS** – You are now prepared to route the other connections on your board. Open the nets spreadsheet and highlight all the nets in the design. Right-click and select **Enable <-> Disable** to make the ratsnets visible for the remaining nets. Refresh the display to clean things up a bit.

Before beginning routing in earnest, it is helpful to change a few settings. Open the **System Settings** and make the following changes: **Visible Grid** = 10, **Routing Grid** = 5, and **Via Grid** = 0. Next, select **Options Dust Preferences** and check **Allow DRC Errors** under **Global Preferences**. You may have to check the box labeled **Activate Online DRC**. The box with the dashed line will reappear. While DRC is on, you will only be able to place routes inside this box, but Layout will inform you if any spacing errors occur while you are routing. This will help you limit the number of errors that you will have to clean up later. You can resize the DRC box by pressing "**B** and draw ing a new rectangle.

Let s route a connection. Turn on the Edit Segment Mode or Add/Edit Route Mode. The two have some subtle differences. Experiment with both to see which one you are most com fortable w ith. Let s start by routing the connection for the pushbutton sw itch. Zoom in a bit and click on the ratsnest near pin 4 of the switch. Left-click to place a segment of a route. When you get near to pin 3, you can press "F to have Layout finish the trace for you. P ins 3 and 4 should now be connected. Now connect the resistor and capacitor that are nearby.

When routing you will want to refresh the display occasionally to redraw the ratsnests. Now connect the resistor to the PLD. Since our traces on the top layer are already oriented horizontally, let's place this vertical route on the bottom layer. When you begin the route, press, 2 to switch to the bottom layer. Since the resistor is a thru-hole part, there is no need for vias in this situation.

**IMPORTANT NOTE:** It is a good design practice to keep routes on one layer oriented in the same direction. For example, you might want to have all traces on the top layer oriented horizontally, while all routes on the bottom are oriented vertically. Doing this increases the number of vias that are needed, but makes routing much easier, especially in very dense designs. After routing is complete, you can go back and remove unnecessary vias. Of course, sometimes it will be impossible to adhere to this guideline.

Route the trace to the top of the PLD. When you get near the top, you can press "V to place a via. Then you can switch to the top layer to complete the trace.

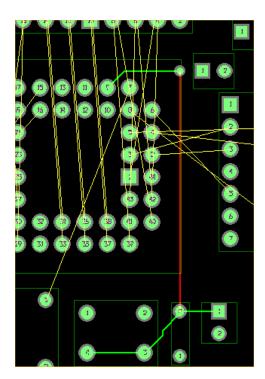

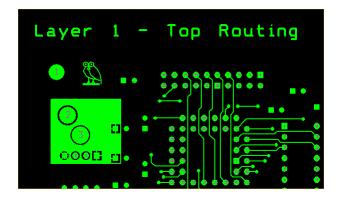

You now have your first complete route. You can begin to finish the other connections. Start by routing one component at a time. For example, you might route the TIL311 next, as is shown above. It is also important to route critical signals first, such as clocks and resets. Remember that you can zoom and pan during operations such as routing. The DRC routing box will move with you. With the current DRC settings, you may sometimes see circles around your traces if you get too close to another net or pad. If this happens, then Layout is warning you that you are making a spacing violation with your route. You will need to fix it. I would also suggest that you browse the shortcut keys in the help to see which shortcuts will be useful during routing. When you are done routing, your design may look something like this.

Congratulations! All the really hard work is done. Now there are just a few remaining steps to complete your board for submission to a board shop for fabrication.

**8.5 PERFORMING ECOS & BACK ANNOTATION** – What if you wanted to make some changes to your design while you were in Layout? OrCAD provides the means for this through ECOs (Engineering Change Order) and back annotation. An ECO is used when changes are made in schematics (perhaps you added some more circuitry or changed some connections). Back annotation is used for changes made during Layout.

When you saved your file, Layout reminded you to back annotate. This was because we added the mounting holes to our design, and OrCAD wants to export those back to schematics. Even though it is not entirely necessary right at this moment, let s step through the process so you know how it works. On the menu click Auto-Back Annotate. OrCAD will create a swap file called Elec424Tutorial.swp in your board directory. It is safe to overwrite your existing board file with the new one. Look at the swap file in Notepad. You will see several sections. One thing that Layout does is update part and net properties (such as its coordinates) in Capture. If new components were added, then you would also see those changes. Now let s im port this file into Capture. Start Capture and highlight your dsn file. Select Tools-Back Annotate... You can leave the Scope and Mode settings untouched. Use the Browse button to find your swap file. Click OK to start the update. Occasionally, when you add components like mounting holes, you will get an error during back annotation. This is usually safe to ignore.

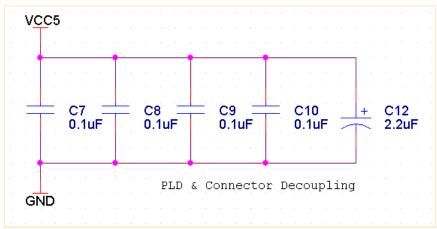

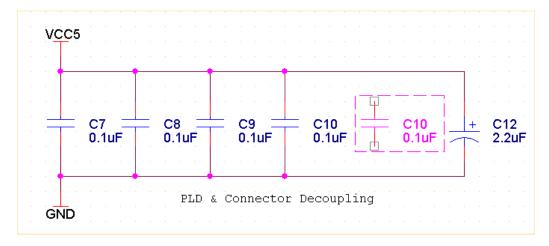

Now let s go the other direction. Perhaps we have one to many decoupling capacitors, so we will remove one. On page 2 of your schematics, delete on of the decoupling capacitors.

Next, save the design and regenerate the netlist as described previously. Close your board in Layout, but keep Layout running. In Layout select **Tools**→**ECOs**→**Auto ECO**. First, you will be asked for your

original board file. Find the Elec424Tutorial.max in your board directory. Second, you will be asked for the new netlist that just created. file you Find Elec424Tutorial.mnl file in your sch directory. Finally, you will be asked for a lis file to write to. This file is just a report of the ECO, and it is safe to overwrite the existing one in your board directory. When the ECO is done,

you will see the **lis** file in Notepad with a report of what happened during the ECO. You will also be prompted to save the new board file. If the report looks OK, then go ahead and overwrite your existing board file. In our example here, we deleted **C11**, so the report should look something like the diagram on the left. If you open the new board file, you will see that capacitor **C11** is no longer in the design.

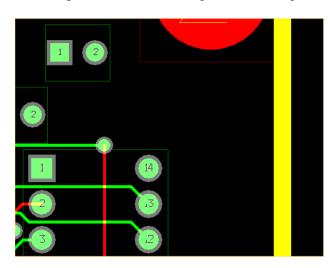

Before ECO After ECO

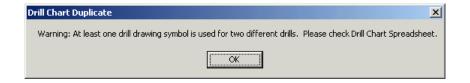

When you open your board after an ECO, you may get the following message.

Just click **OK**. We will fix this problem a little bit later.

Deleting this part was just a demonstration. We really want that capacitor in our design, so let s put it back. Adding new components to a design requires a little more caution than deleting components. Open up page 2 of your schematics and cut and paste one of the other decoupling capacitors.

When you cut and paste a component, every property gets copied, including the reference designator. This design now has two capacitors called **C10**. If you were to try and perform an ECO right now, it would cause much confusion. Double-click the new capacitor and change the reference to **C?**.

**IMPORTANT NOTE:** A fter L ayout has begun, any new parts in schematics should be given a "? in the reference designator. Then let C apture s annotation utilities give a new number to the part.

Since we have some new parts, we need to annotate the design again. Perform an incremental reference update as you did before. The new part should now have a number. Regenerate the netlist and start an ECO. When done, the part should be back in the design. However, when we cut and paste parts, all properties are copied, and this includes x and y locations on the board. Our new part is probably sitting right on top of another part. Use the components spreadsheet to locate the new part. Give it a new and safe location such as 0,0 and then use the **Component Tool** to place it in the proper location. You could also avoid this problem by resetting the coordinate properties in Capture before regenerating the netlist.

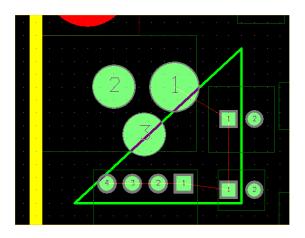

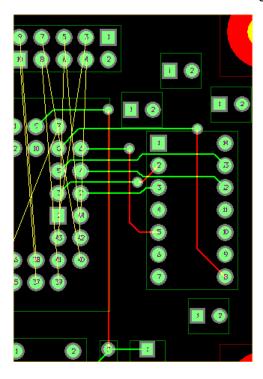

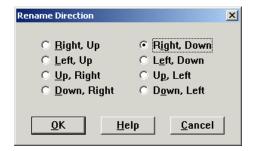

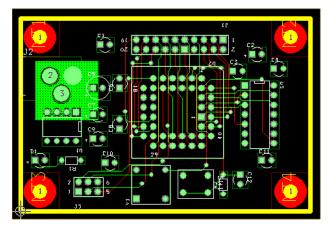

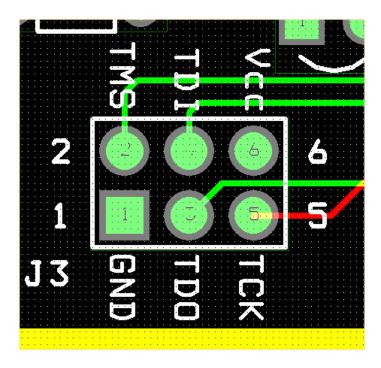

You will often use ECO to do forward-annotation, but there are only a few occasions where you may want to perform back annotation. One such instance is to rename components. Right now, all the components in your design are named according to their order in schematics. However, in a larger board, it will be very hard to tell where a specific component is during debug. The components on the board will seem to be named in a random manner. Layout can rename your components for you, which will make finding them on the board much easier. To see the results of this operation, make the silkscreen layer visible again (SST). Select Options >C om ponents Renam ing... and choose Right, Down... in the Rename Direction dialog.

Next, choose Auto→Rename Components. You silkscreen should look a lot different now.

**Before Renaming**

**After Renaming**

Since you have changed the reference designators in your design, you need to generate a swap file and perform back annotation. You should do this **IMMEDIATELY**. If you don t, it can cause some serious problems for you later in the design. When you read the swap file into Capture, you may get errors on renaming the mounting holes. It is safe to ignore these.

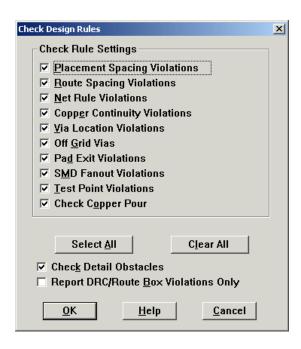

8.6 CHECKING FOR ERRORS – The next step in the design process is to check for any spacing errors. Or CAD uses the spacing variable that you set earlier to determine if there are errors in your design. We used 10 mil spacing from all features as a minimum for this design. To perform a Design Rule Check (DRC) choose Auto→D esign Rule Check... from the menu.

Make sure all the **Check Rule Settings** are checked and click **OK**. Your design will rarely contain no errors, and you will need to look at the errors spreadsheet to see what the errors are. Some can be safely ignored.

| Error Markers |                   |                      |

|---------------|-------------------|----------------------|

| Location      | Туре              |                      |

| [200,1800]    | Pad Spacing Error | "MT1.1"; Obstacle 18 |

| [2800,1800]   | Pad Spacing Error | "MT2.1"; Obstacle 18 |

| [200,200]     | Pad Spacing Error | "MT3.1"; Obstacle 18 |

| [2800,200]    | Pad Spacing Error | "MT4.1"; Obstacle 18 |

|               |                   | ,                    |

In this example there are four Pad Spacing Errors, one generated by each of the mounting holes. In this case OrCAD is complaining because the place outline for the part is on the edge of the board. This error is OK to ignore. If there are errors that need to be fixed, you can delete the marker from the spreadsheet. Let s generate a route spacing error so you can see what it looks like. These are the most important. Move a trace anywhere in your design so that it conflicts with another trace or pad.

Now rerun the DRC. The new errors should appear in the spreadsheet.

| Туре                | Comment                                                                                     |

|---------------------|---------------------------------------------------------------------------------------------|

| Pad Spacing Error   | "MT1.1"; Obstacle 18                                                                        |

| Pad Spacing Error   | "MT2.1"; Obstacle 18                                                                        |

| Pad Spacing Error   | "MT3.1"; Obstacle 18                                                                        |

| Pad Spacing Error   | "MT4.1"; Obstacle 18                                                                        |

| Route Spacing Error | "J1.3" to "U2.1" Net "PLDIO1"; "J1.4" to "U2.44" Net "PLDIO44"                              |

| Route Spacing Error | "J1.4" to "U2.44" Net "PLDIO44"; "J1.3" to "U2.1" Net "PLDIO1"                              |

|                     | Pad Spacing Error Pad Spacing Error Pad Spacing Error Pad Spacing Error Route Spacing Error |

You can remove the errors by moving the trace back to its original position. Once the error has been corrected, you can delete the marker from the errors spreadsheet. Do not try to use the **Auto→Remove Violations** tool. It is tempting, but it will actually rip up offending traces and move parts. You will end up having to do a lot of cleanup and rerouting after using this tool.

8.7 CLEANING UP & THE DESIGN - Now it is time to clean up your design. You should think of your board as a work of art. Other people may look at it, so you want it to look nice. Furthermore, a clean design will ensure fabrication success. When cleaning the design, the following should be kept in mind.

A. Route Spacing - You have set a minimum of 10 mils for feature spacing in your design. However, do not pack traces closely together unless you have to. First, you can push the manufacturing limits to far and some of your boards may come back bad. Second, routing traces closely together is generally a bad idea because this can result in undesired mutual inductance between traces.

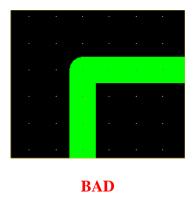

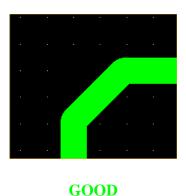

**B. Right Angles in Traces** – D on t use right angles in routing your traces. M iter the corners.

**C. Pad Exits** – Trace exits from pads should be clean and not come out of the pad at unusual angles.

**D. Remove Extra Vias** – Vias add cost to a board, so it is a good practice to remove any unnecessary vias from your design.

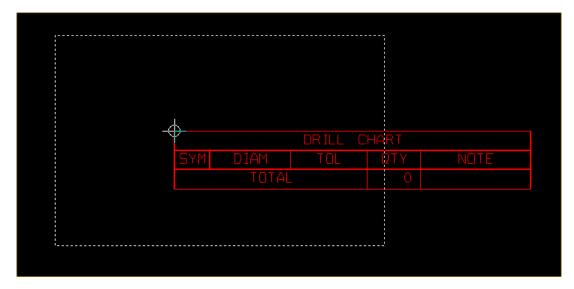

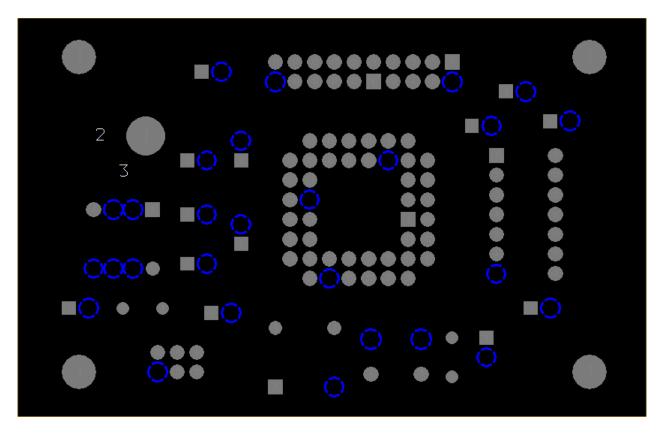

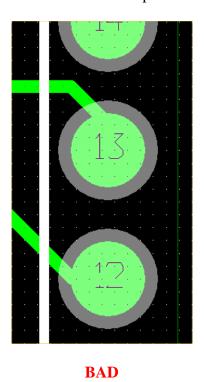

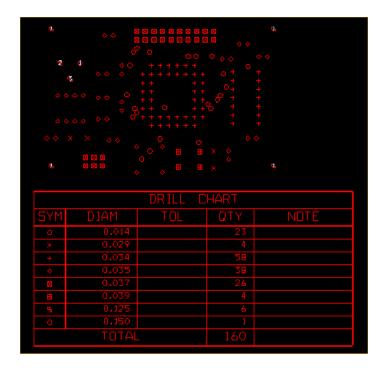

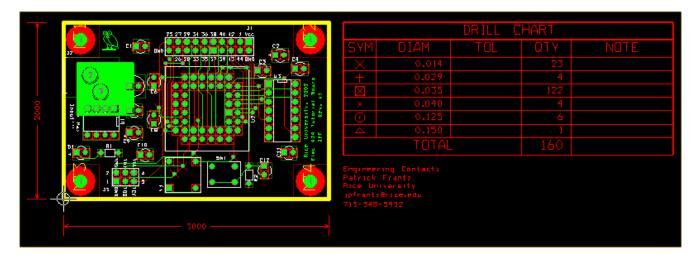

**E. Drills** – Drills require some special attention. First, you need to fix the error you got earlier about the drills. This error occurs sometimes after you perform an ECO. To see the problem, make the **Drill Drawing (DRD)** layer visible. Press **Backspace** to clear the display and then **Shift-5** to display just the **DRD** layer.

The **DRD** layer is a documentation layer that contains a chart with all your drill sizes and their locations on the board. The problem is that two drills are using the same symbol. In this case it is the 14 mil drill and the 150 mil drill. To fix the problem, click **View Spreadsheet** and select **Drills** to view the drills spreadsheet.

| Drill Size | Symbol | Tolerance | Note |

|------------|--------|-----------|------|

| 13         | 17     |           |      |

| 29         | 11     |           |      |

| 34         | 12     |           |      |

| 35         | 13     |           |      |

| 37         | 14     |           |      |

| 39         | 15     |           |      |

| 125        | 16     |           |      |

| 150        | 17     | ·         |      |

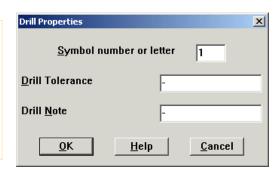

You can double-click the **Drill Size** cell to adjust the **Drill Properties**. I suggest starting with symbol **1** for the 13 mil drill and incrementing from there. When you are done, you should have symbols **1** to **8**, and you will no longer get the error when you open your design.

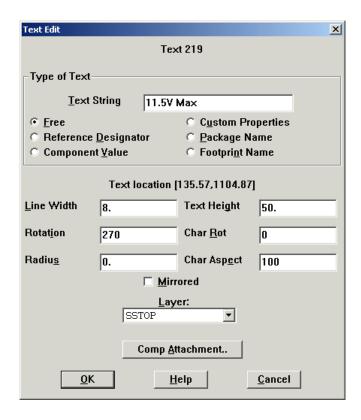

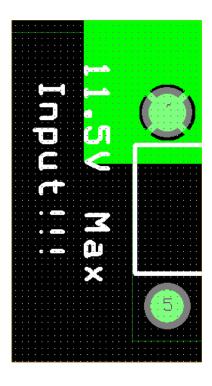

There is one other thing that needs to be done with regard to drills. Some board shops have limitations on the sizes of drills. The board shop we are using for this project offers only 16 drill sizes<sup>7</sup>. They have programs that will scan your Gerber files and automatically adjust the drill sizes for you, but to avoid any problems it is wise to give them files with the correct sizes in the first place. This way you can be sure that your board will be manufactured exactly as you send it. It is also a good practice to consolidate drills anyway. In this design, we might try to adjust the footprints so that the 34 and 35 mil drill sizes are the same. The board shop will only have to use one drill bit, and this will save money.